Setup and Hold Time - Part 3: Analyzing the Timing Violations

- saumil vora

- Sep 15, 2020

- 6 min read

In the previous blog on STA (Setup and Hold Time - Part 2), details given in the timing report were discussed. To understand the timing report is very important because, in case of timing violations, the first task is to analyze the timing reports. By analyzing the timing report one can reach the root cause of the timing violation. There can be multiple reasons for the timing violation. How to find the root cause of the violation? How to fix it? These two are the major questions that STA engineers have to address. This blog will mainly focus on the approach to find the source of the timing violation and a few techniques to fix them. In physical design, there can be multiple solutions for a similar kind of problems. Sometimes, the same problem in two different partitions cannot be fixed using the same solution. The designer has to choose a solution based upon the nature of the block/partition owned by them. So, techniques to fix timing violations discussed here can be helpful but are not limited. There can be several other ways to fix the problem which can be learned from experience.

Analyzing the Setup Timing Violations

What should be the approach if we come across the setup timing violations in the design? A very common question asked by the engineers new in this domain. Below is the step-by-step approach to analyzing the timing path.

Firstly lookout for data tran, data cap, and high fanout violations. Fixing these violations will help to reduce the setup timing violations in a few paths.

From the setup timing report check for the start point, endpoint, and the path group of the violating paths.

If violating paths are having the common start point and multiple endpoints then analyze the common path. We can use the path grouping technique here. Create a separate path group with the violating paths and increase the optimization weightage for these paths. The PnR tool will try harder to fix these paths. Commands for path grouping can be found from the command manual of the related CAD tool.

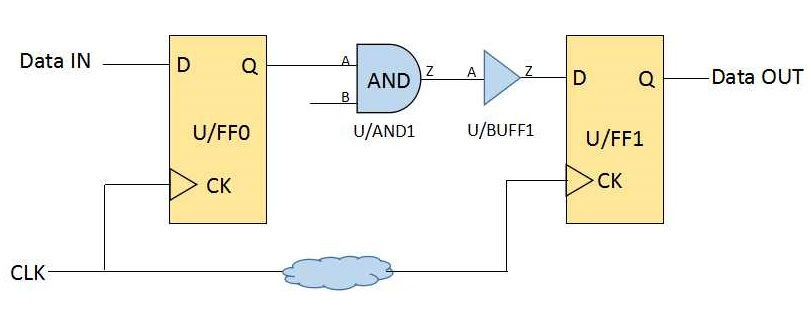

The next thing to check is the logic depth. If more combinational cells are placed in between the launch and the capture flop then it may lead to setup timing violation. One should check if possible to fix the violation by sizing the cells properly or by using buffers in the path. If this is not helping then need to go for logical restructuring.

The next thing to analyze is the hierarchy split. If the cells belonging to the same module/hierarchy are placed apart from each other then route length will increase. Longer routes can cause setup timing violations. If there is any hierarchy split in the design then one should identify the reason using fly-lines analysis. The designer can also create a bound with sufficient area to avoid the split in the module (hierarchy).

If crosstalk analysis is carried out then look out for the crosstalk effect on the path under analysis. If the impact due to crosstalk is more then nullify the crosstalk effect first.

Sometimes the tool will insert too many buffers or inverters pair to meet some requirements. This will add to the data path delay. After properly analyzing, if there are too many buffers or inverters pair in a path then removing a few of them will help in reducing the data path delay which will be helpful to meet the setup timing requirements. Need to make sure that after removing buffers/inverters any other violation should not rise in the design.

All the above techniques are related to the data path optimization. After performing all possible data path optimizations if the setup timing violation is not getting fixed then we can check the clock path as well. We need to be very cautious while playing with the clock path because a small change in the clock path can have an impact on many paths in the skew group.

Check the local skew for the paths with the highest negative slack. Too large skew can also reason into a setup violation. Try to reduce the skew without impacting the other paths.

One can also go for the useful skew technique if enough margin is available in the subsequent path.

A very rare but useful technique is to use a latch instead of the flip-flop either at the launch or at the destination position depending upon the active edge of the latch and the nature of the timing violation. This technique should not be used if we can achieve good results using any of the above methods.

In the cell library, flip-flops with less setup timing or with negative setup timing are also available. In a worst-case scenario, the designer can also use these flip-flops to overcome the setup timing violations.

If for any path, the setup is not getting fixed even after trying all the possible techniques, the last option is to reduce the frequency. During the entire STA analysis, we have assumed the worst-case scenarios and pessimistic delays are considered for all the cells and the data paths. In this situation, if a very small amount of negative slack is still present then also we can go for tape-out. Even after fabrication, if we see setup timing violation then reducing the operating frequency can help to meet the requirements.

Analyzing the Hold Timing Violations

Hold timing violations can mainly occur due to less delay in the data path. There can be multiple reasons for this let us discuss them one-by-one.

Some combinational paths have very few logic cells. In this case, the data transfer takes place at a very high speed. This creates the hold timing violations.

In another case, there are paths where there are no logic cells between the launch and the capture flop. In this scenario, there can be memories also at the capture side.

For both the above scenarios, increasing the delay in the data path is the only solution. This can be done either by down-sizing the existing cells in the data path or by adding buffers or delay cells in the data path.

As hold timing check is done at the same clock pulse, changing the clock frequency won't help here. But we can play a bit with the skew to reduce the hold violations. The negative skew is useful in the hold which means we can increase the delay for the launch clock path and reduce the delay for the capture clock path. This will help to meet the hold timing requirements.

It is highly recommended to fix all the hold violations in the design. Unlike setup violations, here we cannot control hold by changing the frequency so if a hold violation is existing after fabricating the chip then there is no way to fix it. That entire chip is a waste.

Setup and Hold Violations in the Same Path

In general, the setup timing is checked at the worst-case scenario while the hold timing is checked at the best-case scenario. A situation can arise wherein setup and hold both are violating for the same path in their respective scenarios. What can be the reason for this? Discussed below.

There are cells in the data path which shows the huge variation in delay from the worst-case scenario to the best-case scenario.

Due to the crosstalk effect, we can observe both, the setup and hold violations in the same path.

The next question that comes into mind is what should be the approach to fix this type of violation? Few points are mentioned below.

The first priority should be to overcome the crosstalk effect if exists. This will relax the situation somewhat and will be easy to fix the remaining violations.

Check out for the start point and endpoint of the violating path. If there are different endpoints for the setup path and the hold path then it will be easy to fix the violation. In this case, find out the diverging point in the path and apply fixes after that point.

If the start point and endpoint are the same then in that case first try to fix the setup violation with some extra margin then go for fixing the hold timing. In this scenario, while fixing the setup hold will degrade and while fixing hold setup will degrade. This is a tricky situation. Here choose the cells whose delay does not vary much in the worst-case and the best-case scenarios.

In any situation, it is highly recommended to fix the hold violation. If in the worst case, the setup timing issue is not getting fixed then also we can deal with it but there is no relaxation for the hold timing violations.

These are the few methods to fix the timing violations. For any feedback or discussion please mention your views in the comment section below.

To read other blogs on physical design concepts click on the below links.

Comments